Product Summary

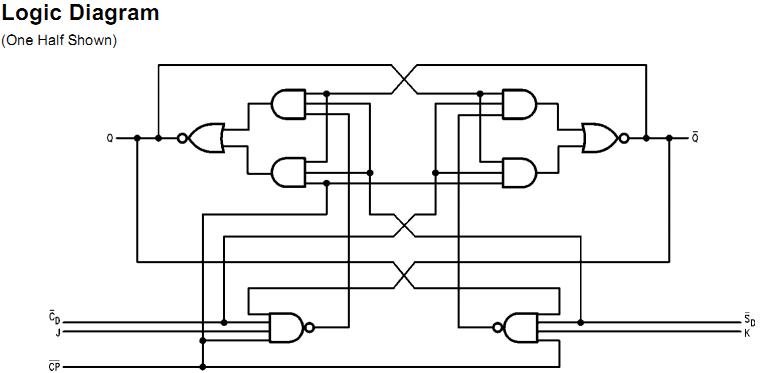

The 74F112PC is a Dual JK Negative Edge-Triggered Flip-Flop. The 74F112PC contains two independent, high-speed JK flip-flops with Direct Set and Clear inputs. Synchronous state changes are initiated by the falling edge of the clock. Triggering occurs at a voltage level of the clock and is not directly related to the transition time. The 74F112PC J and K inputs can change when the clock is in either state without affecting the flip-flop, provided that they are in the desired state during the recommended setup and hold times relative to the falling edge of the clock.

Parametrics

74F112PC absolute maximum ratings: (1)Storage Temperature: -65 to +150℃; (2)Ambient Temperature under Bias: -55 to +125℃; (3)Junction Temperature under Bias: -55 to +150℃; (4)VCC Pin Potential to Ground Pin: -0.5V to +7.0V; (5)Input Voltage: -0.5V to +7.0V; (6)Input Current: -30 mA to +5.0 mA; (7)Voltage Applied to Output in HIGH State (with VCC = 0V), Standard Output: -0.5V to VCC; 3-STATE Output: -0.5V to +5.5V; (8)Current Applied to Output in LOW State (Max): twice the rated IOL (mA).

Features

74F112PC features: (1)Mounting Type: Through Hole; (2)Package / Case: 16-DIP (0.300 inch, 7.62mm); (3)Function: Set(Preset) and Reset; (4)Number of Bits per Element: 1; (5)Number of Elements: 2 ; (6)Output Type: Differential; (7)Trigger Type: Negative Edge; (8)Type: JK Type; (9)Packaging: Tube; (10)Delay Time - Propagatio:n 5ns; (11)Frequency - Clock: 105MHz; (12)Lead Free Status: Lead Free; (13)RoHS Status: RoHS Compliant.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

74F112PC |

Fairchild Semiconductor |

Flip Flops Dual J-K Flip-Flop |

Data Sheet |

Negotiable |

|

||||

|

74F112PC_Q |

Fairchild Semiconductor |

Flip Flops Dual J-K Flip-Flop |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))